RF IC設計ツール (RF IC Design Tools)

2022/2/13 by T. Hirano

COMSOL Multiphysics (RFモジュール)アプリケーションビルダーで開発したアプリ(exe)ファイルを公開していきます。

※ 本ページの電磁界シミュレータCOMSOL Multiphysicsに関するお問い合わせは計測エンジニアリングシステム株式会社(KESCO)[1]にお願いいたします。

※ 本ページの内容についての感想等、共同研究等のご相談がありましたら、thirano(AM)tcu.ac.jp ((AM)は@)または本ページ下部のフォームにてご連絡ください(フォームは確認が遅れる可能性があります)。

※ COMSOL Multiphysics RFモジュールは有限要素法による電磁界解析を行っており、理論については[2]で解説しています。

※ ZIPファイルにはCOMSOL Application Builder Compilerで作成した実行可能なWindows用EXEファイルが入っています。作成方法の説明は[3][4]をご覧ください。

※ COMSOL Multiphysicsのアプリケーション・ビルダー・コンパイラで作成したEXEファイルはWindowsで実行可能です。初回の起動時のみ、COMSOL社のサイトからライブラリをダウンロードしてインストールする必要があります(ダウンロードは自動的に始まります)。他にもいろいろな電磁界解析規範問題について解説したサイト[3]をご参照ください。 |

COMSOLアプリEXEファイル

| 解析対象 |

構造 |

説明/各シミュレータのファイル |

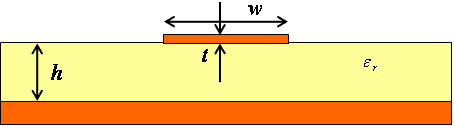

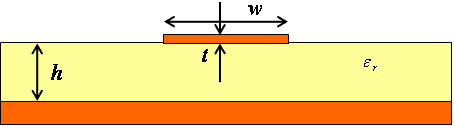

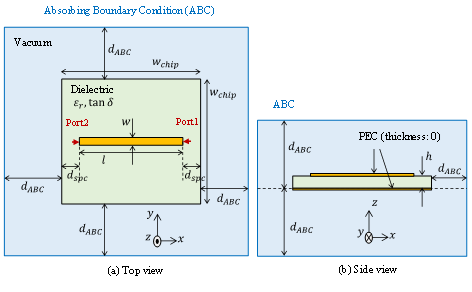

| マイクロストリップ線路(MSL) |

εr=4.5, tanδ=0.04

h=1.57 mm, t=0.001 mm, w=3 mm |

通常、50ΩのMSLを設計します。左図のh, tは変化させられないので、wを変化させて50Ωとなるようにします。

MSLの近似式による設計で十分良い精度が得られますが、シミュレータでも確認します。

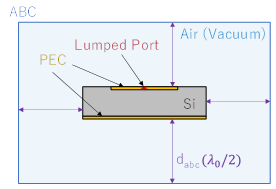

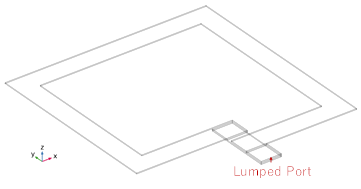

ポートのサイズが波長よりも小さいとき、集中ポートが使えます。ここでは、MSL両端を集中ポートで励振した場合のFEM解析です。

msl_pec_lump_port2.zip

comsol_msl_lumped_port.pdf (説明) |

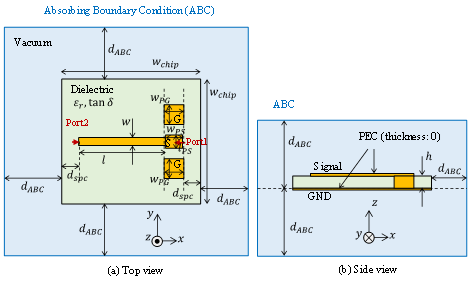

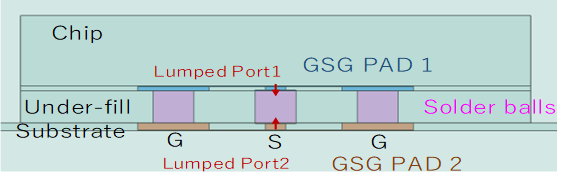

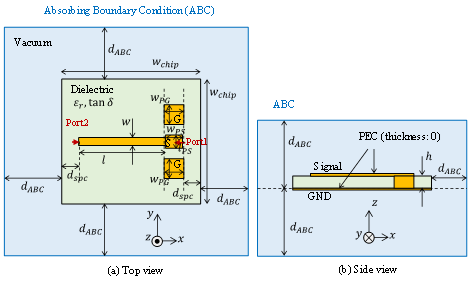

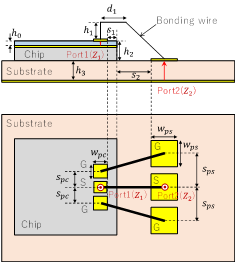

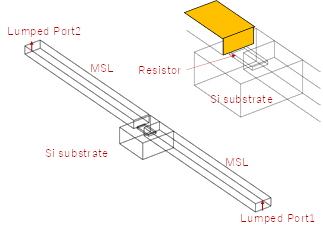

| パッド |

(a) RF PAD (GSG)

(b) MSL |

パッドはチップの信号を外部に出すための電極です。チップの回路層最上層の上の表面はSiO2やSiNなどの保護膜で覆われていますが、パッド部分のみ、電極(Alが多い)を露出させています。回路層内で作成した線路の信号を外部に取り出すために、パッド構造による特性劣化の影響がないか気になるところです。左の(a)はGSGパッドをモデル化したシミュレーションです。Gパッドはグランド(GND)の略で、下部のGNDに金属で接続されています。Sパッドは信号線(Signal)で、GNDには接続されておらず、MSLにつながっています。パッドなしの(b)のモデルと比較して結果の差異が無視できればパッドは上手く出来たと考えられます。考えられる影響としてはSパッドにGパッドが近づいても大丈夫かどうかということです。ところで、(a)の電磁界シミュレーションモデルではMSLのGNDからSignalに対して集中ポートを設定しています。測定ではプローブ、実装ではボンディングワイヤやフリップチップで行いますが、このような理想化した解析モデル化でいいのか気になると思います。この問題についてはプローブ先端の電界分布に近いモデル、つまりGパッドからSパッドに対して集中ポートで励振したモデルなどいろいろ試し、結果的にこのように下部のGNDからSignalに垂直に集中ポートで励振するモデルでも差異が小さいことを確認しています[5]。

Model (a): rf_pad.zip

Model (b): msl.zip |

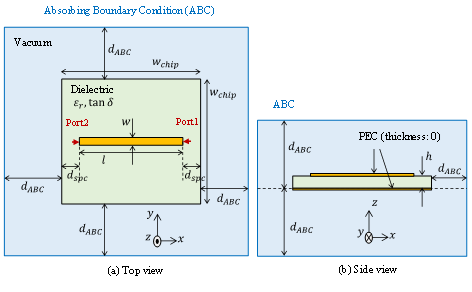

| ボンディングワイヤ |

|

チップとパッケージ(基板)を接続する1つの方法がワイヤボンディングです。チップ上のパッドからパッケージの金属まで曲がった導線(柔らかい金Auなど)で接続されます。

wire_bonding.zip |

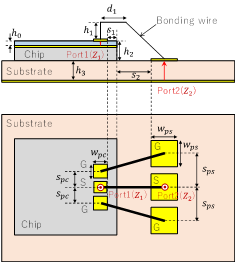

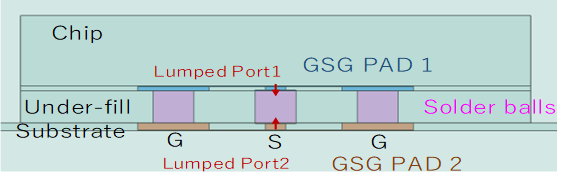

| フリップチップ |

|

フリップチップ実装のシミュレーション。チップ、基板ともGSGパッドを間の伝送特性を評価しています。

flip_chip.zip |

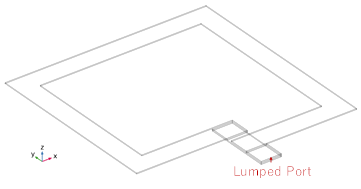

| キャパシタ |

|

MIMキャパシタのシミュレーション。これは簡易モデルですが、真面目にモデル化すれば線路や基板との結合も評価できます。

capacitor_mim_1port.zip |

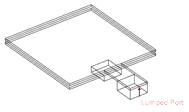

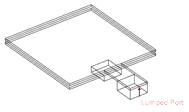

| インダクタ |

|

方形1回巻きのオンチップインダクタのシミュレーション。これは簡易モデルですが、真面目にモデル化すれば線路や基板との結合も評価できます。

inductor_rect_1turn_1port.zip |

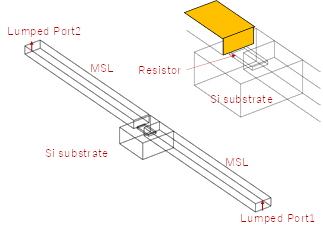

| 抵抗 |

|

シリコン基板上の抵抗のシミュレーション。線路や基板との結合も評価できます。

resistor.zip |

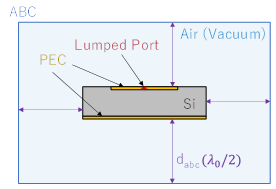

| オンチップアンテナ |

|

Siチップ上のオンチップダイポールアンテナ。放射効率は放射電力/入力電力で計算できます。

on_chip_dipole_antenna.zip |

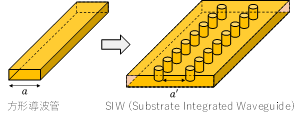

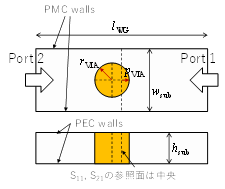

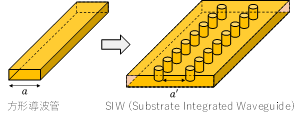

| SIWのVIA設計 |

|

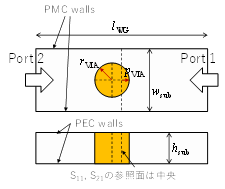

導波管壁を誘電体基板にVIA(金属メッキの穴)で作るSIW (Substrate Integrated Waveguide)の設計ツールです。VIAの列で導波管の横壁を作るので、等価的に完全な金属壁の導波管幅aを実現するためのVIA間隔a'は少し異なります。これを計算するためのツールです。上図のようにVIA1つを取り出したモデルを考えます。縦方向(VIAの円柱軸)の方向の電界を漏らさない構造なので、横壁を磁気壁(PMC)、上下はモデルどおり電気壁(PEC)としてTEM波を入射させ、反射係数S11を計算します。振幅|S11|が十分大きくなるようにVIA間隔を狭め、位相arg(S11)が金属壁と同じ180°になるようにオフセットpVIAを調整します。

【設計用】

siw_via_design.zip (VIA1列)

siw_via2_design.zip (VIA2列)

【全体解析】

siw_wg.zip (VIA1列)

→同じ長さの方形導波管のS21が一致していれば(特に位相に注目)、上手く設計できたことが確認できます。 |

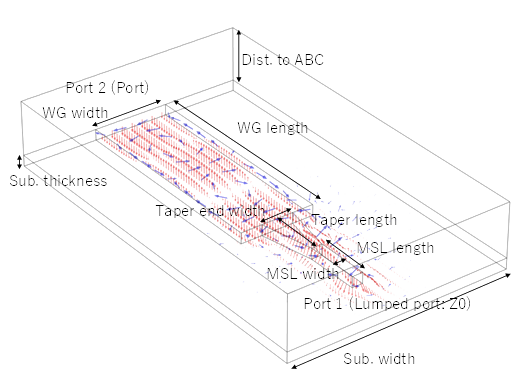

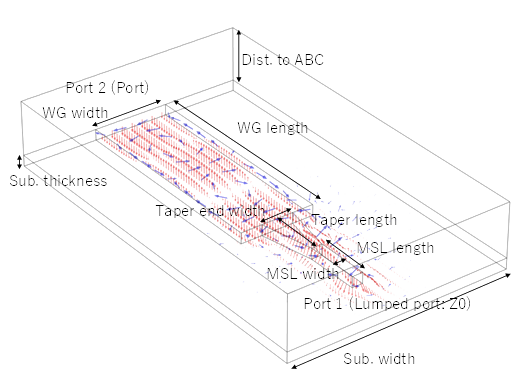

| MSL-WG変換器 |

|

MSLからSIWに入力する祭によく用いられる構造です。

msl2wg_transformer.zip |

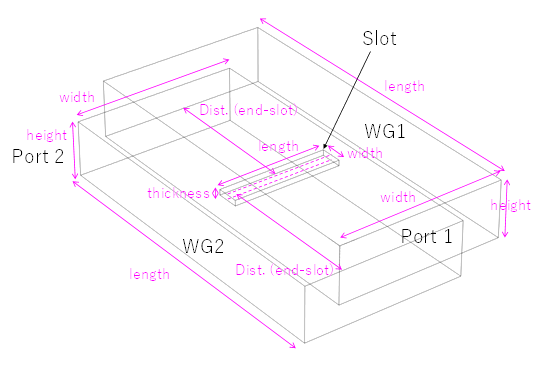

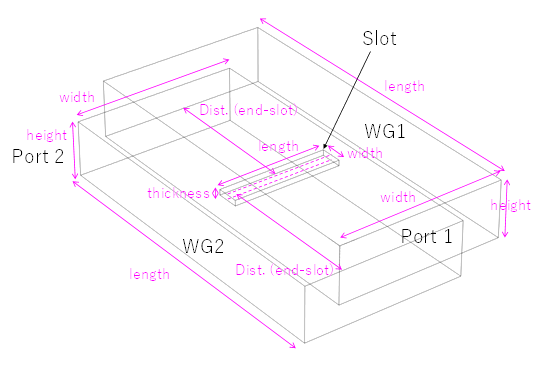

| WG-WG変換器 |

|

広壁結合導波管-導波管変換器です。

wg2wg_transformer.zip |

| ダミーメタル |

|

公開未定 |

関連リンク

- 計測エンジニアリングシステム株式会社(KESCO)

- 平野拓一, 有限要素法による電磁界シミュレーション −マイクロ波回路・アンテナ設計・EMC対策−, ISBN:9784764960121, 近代科学社,

2020年9月. (理論および詳細説明はこの本をご覧ください)

- 平野拓一: 電磁界規範問題および市販シミュレータのファイル例

COMSOL Multiphysics Application Builderを用いたアプリケーションの作り方(ダイポールアンテナ解析の例)

COMSOL Multiphysics Application Builderを用いたアプリケーションの作り方(ダイポールアンテナ解析の例)

- T. Hirano, K. Okada, J. Hirokawa, and M. Ando, "Accuracy Investigation

of De-embedding Techniques Based on Electromagnetic Simulation for On-wafer

RF Measurements," InTech Open Access Book, Numerical Simulation -

From Theory to Industry, ISBN 978-953-51-0749-1, Chapter 11, pp.233-258,

DOI: 10.5772/48431, September 19, 2012. (Open Access)

半導体・通信の発展の概要

歴史や技術以外の全体像について学ぶことは、技術を学ぶ上でも大変重要であり、また楽しいものです。ここでは半導体技術発展の概要について簡潔に説明します。ただし、半導体、IC、LSIの発展については著者の知識も超えて、とてもこのページで説明しきれないほどの内容なので、詳しくは[1][2]などをご参照ください。

戦後、敗戦した日本は貧しいながらも努力して発展し、技術もアメリカに追いついていく様子が[1][3]で描かれています。その後、起伏はあるものの、順調に発展していきます。1970年代には日本の自動車生産台数はアメリカを抜いて世界No.1になりました。アメリカを抜いたことでアメリカからクレームが入り日米自動車摩擦が起きました。自主規制を行ったりアメリカに工場を作って現地生産(現地の経済にも貢献する)をしたりして関係を保ったようです。1980年代には半導体生産でもアメリカを抜き、スーパー301条としても知られている日米半導体摩擦が起きました。この解決は自動車のように上手く処理できず、現在の日本の衰退につながってしまっています。日本国内の外国製半導体のシェアを20%に引き上げることを目標にしたようで、ここで日本自らが韓国をバックアップしてしまいます(自動車のようにアメリカに工場を作って生産せず、リストラされた社員が土日に韓国に通って安く技術供与してしまい、それが現在のサムスン電子の発展につながっているそうです。韓国の自動車・半導体は日本の技術が流れて発展したものです)。1980年代のバブル経済の時代には"Japan as Number One"とも言われるようになり、自動車、半導体産業とともに経済も(バブルなので実体はかなり空っぽですが)アメリカを追い抜く勢いでした。バブル経済が大蔵省の総量規制をきっかけとしてはじけ、経済も低迷し(実体に戻り?)ました。

しかし、1990年代以降はインターネット、携帯電話などの通信が発展したので、産業・経済構造はその場をしのげていたように思います。ただ、日本の通信規格・販売方式・通信機器はi-modeなど、HTMLの機能限定版を使う独自方式で、後に世界標準規格に従うようになると上手くいかなくなるとガラパゴス(ガラパゴス諸島のイグアナのように閉鎖環境で独特の発展をしている。裏を返せば閉鎖環境を出た世界では生きていけないという意味)と呼ばれるようになりました。それが昔のi-modeなどの折り畳み式携帯電話がガラケー(ガラパゴス携帯)と呼ばれている理由です(本当はこのスタイルの携帯電話はフィーチャーフォンと名付けられています)。日本のガラパゴス状態が崩壊したきっかけは2007年のAppleのiPhoneの登場でした。iPhoneはタッチパネルでMacのOSと同程度の(?)性能のiOSで動いており、電話機能はコンピュータの1つのアプリという設計で、フィーチャーフォンのような低機能なブラウザがおまけのようについた携帯電話よりも遥かに高機能でした。そのため、iPhone型の携帯電話はスマートフォン(スマホ)と呼ばれるようになりました(私は当時、その少し前にNintendo DSの無線通信機能に驚いたので、タッチパネルもあるし、気付いたら技術的は寄せ集めれば出来そうだったのになと思いました)。Appleは機能だけでなく、デザインやユーザーインターフェースにもこだわるので、見た目の格好良さが市場で大ヒットし、日本でもスマートフォンのシェアが拡大していきました。iPhoneの登場後も日本ではすぐに追いついて開発しようとする勢いがありませんでした。それは大手キャリアの販売店経由でしか携帯電話を売れないという独自販売方式(本来高い機器を、利用料で回収していたこともある)が原因で、メーカーは独自にスマートフォンを開発したとしても売る環境がなかった、売ったとしても大手キャリアが販売する機器よりはるかに高くて売れないことが開発意欲低下の原因です(まさに、ガラパゴスという感じです)。

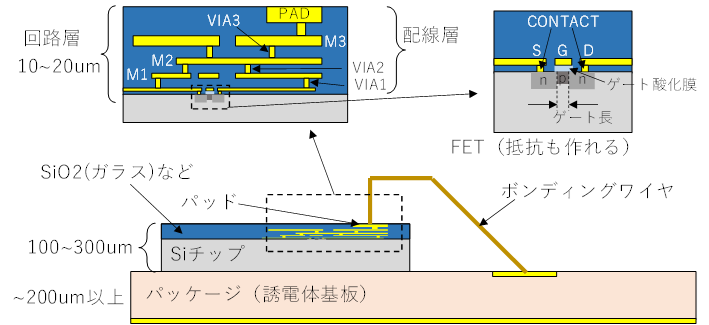

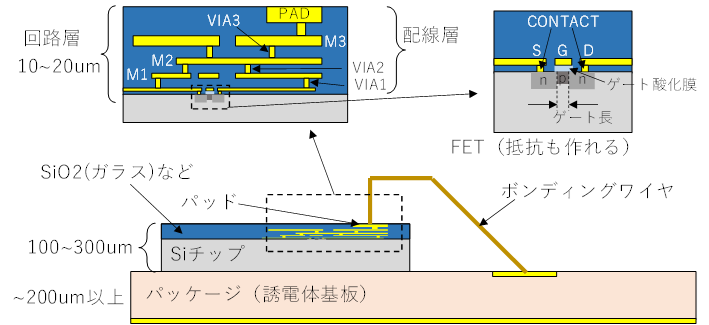

話を半導体に戻します(出てくる用語は下図を見ながら理解してください)。半導体もインターネットの普及により、多くの人がパソコンを使うようになり、ノートPCが登場し、携帯電話に搭載する必要があることでますます発展していきます。この発展、集積密度向上の度合いはインテルの共同創業者の1人であるムーアが予言したムーアの法則(半導体の集積度は18-24カ月で2倍になる)[4][5][6]として有名です。半導体技術も進化を続けるので、さらに微細なものを作って集積度を上げ、同じ面積でも高機能なものが作れるように発展します。半導体のメインの回路素子はFET(電界効果トランジスタ)であり、どの程度小さなFETを作れるかという指標は技術ノード(プロセスノード、技術世代、プロセス世代)と呼ばれます。例えば、180nmのプロセス世代と言ったら、トランジスタのゲート長(下図)が大体180nm程度ということを意味します(正確には180nmがゲート長を表すのかどうかは、各社定義が曖昧なようで、STI

(Shallow Trench Isolation)間隔を基準にしたりすることもあるようです)。180nmの次のプロセス世代は何nmかというと、集積度2倍、つまり同じ面積に2倍のトランジスタが詰め込まれているので、トランジスタの面積は1/2なので、長さの次元のゲート長は1/√2で180/√2≒130nmとなります。このように、次々に1/√2倍して90nm、65nm、45nm、32nm、22nm、14nm、10nm、7nm、5nm・・・と微細化が続いています。このように、次の目標はしっかり集積度2倍に設定されているのがわかります。半導体関係の企業が合同で作った組織が技術の将来予測を公開しているものがロードマップ[7][8]です。初期の頃はムーアの法則はかなり信頼性の高い予測ができました。例えば、ゲーム機の映像は販売された時代の最先端でなければ売れないので、プレイステーション2用の画像処理プロセッサEmotion

Engineの開発では、現在はまだないが将来の生産時には開発されるであろうプロセスで作ることを想定して回路設計していたことが[9]の記事にも書かれています。また、Pixarの歴史について書いた記事[10]には"Then,

at last, Moore's Law saved us. The ever-falling cost of processing power

finally made The Movie economically feasible."とあります。当初は比較的簡単であった微細化も、原子のサイズが無視できない大きさになってくることから途中からは一筋縄ではいかなくなります(それでも、まだ微細化が続いて、本当に原子数個レベルの制御ができるようになっていることは驚愕です)。例えば、65nmから45nmのプロセスに移行するときは、ゲート電極の絶縁体として使われるSiO2(ガラス)のゲート酸化膜(下図)は厚さが1.2nm(5原子程度)になってしまい、リーク電流が大きな課題となっていたそうで、その問題を乗り越える苦労が[11]に書かれています。また、25nm程度よりもゲート長が小さくなった場合には平面型トランジスタではなく、3次元構造のトランジスタFinFETが使われます[12][13][14]。さらに微細化が進むと積層ナノシートトランジスタ[15]が考案されています。ところで、半導体ではFETが主役ですが、トランジスタ同士の配線もまた高い集積度です。配線層はシリコン(Si)の表面の上に形成されており、多段になっています。プロセス世代が進むごとに配線層の数も増えて、現在では10層以上となっています(例えば、[14]や[16]を参照してください)。一般に、上の層ほど厚い配線になっています。1層あたりの厚さは1umあるかないかです。多層配線層を形成するには1層ずつ積み上げていくわけですが、その際に各層の平坦度は高い精度が要求され、CMP(Chemical Mechanical Polishing; 化学機械研磨)行程が入ります。液剤を塗って平坦に研磨する工程で、この際に金属よりもSiO2の方が柔らかく凹んでしまい、後工程に影響を及ぼします。そのため、金属は各層に一定の面積割合を均一に入れないとならないという規則があり、ダミーメタルという小さな面積の金属が多数入ることになります。このような製造上の問題を無くすための規則をデザインルールと言います。シリコンチップの厚さ(ウェハ―の厚さ)は通常300um(0.3mm)程度ですが、トランジスタと配線層を合わせた厚さはその表面の10-20um程度と非常に薄いです。また、微細化されることで動作周波数を上げることができますが、そすると数mm角のチップ内の配線による信号の遅延も無視できなくなってきます。このため、従来は比誘電率4のSiO2(ガラス)が配線間の絶縁体として使われていましたが、より誘電率の低い材料が一部に用いられたり、一部に空気を入れたり[17]しています。

チップ内の微細化は原子サイズが見えてきているからもう不可能だ・・・と言われ続けていますが、様々なブレイクスルーにより微細化が続いてます。チップ内の集積化向上とともに、チップを積層した集積化技術も進みました。TSV(Through-Silicon Via)[18]と呼ばれるもので、チップを非常に薄く削り、ビア(穴を空けて金属で電気的に接続する)を使って複数のチップを積層する技術です。近年、スマートフォンの普及とともに磁気記録のハードディスクドライブ(HDD)が大容量NANDフラッシュメモリのSSD (Solid State Drive)に置き換わっていますが、SSDの大容量化にはTSVの技術が欠かせません。チップを薄く削る技術はCMOSイメージセンサの感度向上にも寄与しています(裏面照射型CMOSセンサー)。従来は回路がある表面から光を照射していましたが、配線層の金属の影響で光が減衰してしまいます。そのため、裏面から光を入れればいいのですが、その代わりに薄く削る必要があるわけです。

高度なグラフィック処理が要求されるようになり、3Dグラフィックス専用のプロセッサであるGPU (Graphics Processing Unit)が登場しました。また、この並列演算はグラフィックのみならず、GPGPUとして汎用計算にも使われるようになりました。今は深層学習の応用が盛んになり、ますますGPGPUが使われるようになっています。NVIDIA等に代表されるような半導体製造工場をもたず、回路設計のみを行う企業(ファブレスカンパニー)が登場し、さらに回路設計(マスクパターン)を元に製造のみを行うファウンドリー(ファブ)の分業が起こりました。代表的なファウンドリーは台湾のTSMCです[19][20]。TSMC創業者のモリス・チャン氏は当初利益を上げられるかどうか自信は無かったそうですが[19]、結果としてこのビジネスモデルは成功しました。GPU以外にもBroadcom、Qualcommなどに代表される通信用のチップなどの需要があったことと、プロセスが微細化するにつれ、工場の設備投資が莫大になって多くの企業が追従できないというのも成功の要因であったと思います。日本の半導体メーカーもこのビジネスモデルに追従しましたが、やはりTSMCは技術は高く、高品質で高い世界シェアを誇っています。台湾の企業は電子機器の製造を受託するビジネスモデルのEDA (Electronic Design Automation)でも鴻海精密工業(日本のシャープが傘下に入り、経営危機を救われることとなった)等の活躍が目立ちます。

(その他、いろいろ懇親会で得た書きたい情報がありますが、書いていいものかどうか気になるものは直接会ってお話したいと思います)

参考文献

- NHKスペシャル 電子立国 日本の自叙伝

- 日本半導体歴史館

- NHK映像ファイル あの人に会いたい「西澤潤一」

- "Gordon Moore: The Man Whose Name Means Progress", IEEE Spectrum,

Mar. 2015.

- "Moore’s Law Milestones", IEEE Spectrum, Apr. 2015.

- "A Better Way to Measure Progress in Semiconductors", IEEE Spectrum, July 2020.

- IEEE International Roadmap for Devices and Systems (IRDS)

- 半導体技術ロードマップ専門委員会

- 斎藤光男: 開発物語「プレイステーション2」用プロセッサ「Emotion Engine」, 電子情報通信学会通信ソサイエティマガジン(B-plus),

Vol.5, No.4, pp.328-333, 2012.

- A.R. Smith, "The Real Story of Pixar," IEEE Spectrum, Aug. 2021.

- "The High-k Solution", IEEE Spectrum, Vol.44, No.10, pp.29 -

35, Oct. 2007.

- "Intel Transistors Enter the Third Dimension", IEEE Spectrum,

May 2011.

- "How the Father of FinFETs Helped Save Moore's Law", IEEE Spectrum,

April 2020.

- "Intel: Back on Top by 2025?", IEEE Spectrum, July 2021.

- "Intel's Stacked Nanosheet Transistors Could Be the Next Step in Moore's

Law", IEEE Spectrum, Dec. 2020.

- "Winner: The Ultimate Dielectric Is...Nothing IBM packs wires in vacuum

to speed chips and save power", IEEE Spectrum, Jan. 2008.

- "GlobalFoundries, Arm Close in on 3D Chip Integration", IEEE Spectrum, Aug. 2019.

- "Next-Gen Chips Will Be Powered From Below", IEEE Spectrum, Aug.

2021.

- "Morris Chang: Foundry Father", IEEE Spectrum, Apr. 2011.

- "TSMC's Morris Chang Says No to Apple, Qualcomm", IEEE Spectrum,

Aug. 2012.

当サイトでは、Google Analyticsを利用してアクセス情報を計測しております。

Back